# Simulation and Prototype Implementation of Hybrid H-bridge MLI with Minimum Switches

A.Ramesh, K.V.S.R.Murthy, B.V.S.S.S.Gopal

Abstract: As the demand for electrical energy increases continuously, we cannot rely on the existing conventional source for continuous power supply, as they are diminishing fast. The renewable energy sources are the best alternative for this energy crisis. We have different types of renewable energy sources and choice of source depends on location and load requirement. The most prominent source is the solar energy because of its own advantages. The nature of supply from this source is DC and it is to be converted into AC for supply to consumers. However, inverters are used for this conversion but produces harmonics. The Multilevel inverters are the alternate choice over conventional inverters due to the advantages of Low dv/dt and lower switching losses. Out of various multilevel inverters, cascaded H bridge (CHB) MLI topology is a well known solution for reducing the harmonics, which needs more number of switches and isolation power supplies which further increases the cost. This paper describes a proposed hybrid H-bridge topology with reduced switches. The proposed topology is implemented in Matlab/Simulink and results for 5, 7, 9 and 11 level are analyzed with their THD in output voltage. Hardware model for 5-level inverter is developed using 8051 micro-controller and results are presented.

Index Terms: Cascaded H-Bridge (CHB), Multilevel Inverter (MLI), Renewable energy source, Total Harmonic Distortion (THD).

### I. INTRODUCTION

Indeed, conventional energy sources supply huge amount of electrical energy, these sources are vanishing fast. Therefore, the world is concentrating on renewable energy sources [1-2]. These sources are free of cost, pollution free and abundant. Out of the available renewable energy sources we are more dependent on solar energy which is continuously available and the present research is concluding that the cost of photovoltaic cell could be going down. With this photovoltaic cell we can get the DC supply. To connect it to the AC grid, DC to AC conversion has to be made, for this we use inverters. The inverters can convert DC to AC but the AC wave form is not a sinusoidal which produces more harmonics. Because, all the converter circuit uses power electronic devices as a controlled switch and the power electronic device have non linear characteristics. To overcome this harmonics problem, the MLIs [3-4] has been introduced. The conventional inverter gives two level output voltage and the MLI is introduced with basic three levels. With an increasing levels the THD could be reduced, at the same time even the number of switches required for this can be increased, which causes more cost.

### Revised Manuscript Received on August 20, 2019.

**Dr. A.Ramesh \***, Professor, Department of EEE, Aditya College of Engineering, Surampalem, India, rameshadireddy007@gmail.com

Dr.K.V.S.R.Murthy, Director (R&D), Aditya College of Engineering, Surampalem. India

**B.V.S.S.Gopal, EEE,** Aditya College of Engineering, Surampalem, India

Diode clamped and flying capacitor types have their own disadvantages like increased amount of diodes and capacitors which increases the cost of inverter. Hence, cascaded H-Bridge (CHB) MLI [5-6] became popular as it decreases the required switches. Here, each H-bridge consists of four switches. The generalized formula for number of levels is 2Q+1. Q is required count of H-Bridges. If we want to get three level output Q=1, and for five level Q=2. With an increase in levels the H-bridges needed also increases which lead to increase in switch count again. Although the number of levels is increased, same problem of increased switching losses happens and cost raises again. Here a bidirectional switch module is developed and connected to the source. The circuits for 5, 7, 9 and 11 are developed in Matlab/Simulink. The analysis is done for same power ratings of R and RL load for each level. The decrease in THD [7-8] as the level increases is also clearly distinguished. There is a possibility to increase the levels beyond 11, but as per analysis it is observed that the decrease in THD for levels beyond 11 is very less. Therefore, in this work I developed a Hybrid H-Bridge MLI up to 11 levels. For validating the simulation results, a prototype is developed for a 5-level Hybrid H-bridge MLI and the results are displayed.

### II. HYBRID H-BRIDGE

Fig.1. Block diagram for PV and Hybrid H-Bridge system.

The above block diagram consists of three units those are PV system, Hybrid H-Bridge and load. The DC output voltage is supplied to the hybrid H-Bridge which converts the available DC to the required AC with a less harmonic content and then it is fed to the load.

### A. Five Level Hybrid H-Bridge

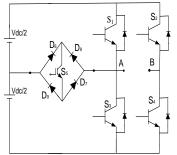

Fig.2. Five level Hybrid H-Bridge

Table I. Switching operation for a five level hybrid

| n-blidge                       |                  |

|--------------------------------|------------------|

| Switches to be                 | Voltage          |

| Turned On                      | level            |

| $S_{3},S_{4}$                  | 0                |

| S <sub>5,</sub> S <sub>4</sub> | $V_{dc}/2$       |

| $S_4,S_1$                      | $V_{dc}$         |

| $S_{2,}S_{5}$                  | $-V_{dc}/2$      |

| $S_2,S_3$                      | -V <sub>dc</sub> |

Fig.2 represents the circuit of a 5-level hybrid H-Bridge MLI. From this 5 switches are required for this topology and the diode bridge is used here for the bidirectional operation of switch. To get each level at any time the number of switches under the operation would be two only. Moreover, the dv/dt rating for each level is  $V_{\rm dc}/2$  only (half of the supply voltage). Therefore the stress on the switches can be decreased.

Table-I represents the operation for the corresponding voltage. Here we have five levels. When  $S_3$  and  $S_4$  are on, then load gets short circuited and the voltage appeared is zero volts. In similar manner only two switches are in operation for each level.

# B. Seven Level hybrid H-Bridge

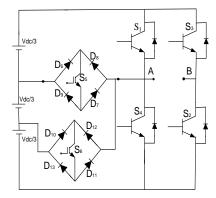

Fig.3. Seven level Hybrid H-Bridge

Table II. Switching operation for 7- level Hybrid H-Bridge

| Switches to be<br>Turned On    | Voltage<br>level |

|--------------------------------|------------------|

| S <sub>2</sub> ,S <sub>4</sub> | 0                |

| $S_{2},S_{6}$                  | $V_{dc}/3$       |

| S <sub>2</sub> ,S <sub>5</sub> | $2V_{dc}/3$      |

| $S_1,S_2$                      | $V_{	ext{dc}}$   |

| S <sub>3</sub> ,S <sub>5</sub> | $-V_{dc}/3$      |

| S <sub>3</sub> ,S <sub>6</sub> | $-2V_{dc}/3$     |

| S <sub>3</sub> ,S <sub>4</sub> | - $V_{dc}$       |

The circuit diagram for 7- level hybrid H-Bridge MLI is mentioned figure 3. In this number of switches used are 6. And another diode bridge circuit is used. The seven level hybrid H-Bridge consists of three symmetrical voltage sources  $V_{\rm dc}/3$  each. Switching operation for 7-level H-Bridge is indicated in Table-II, in which the switching operation for each level is mentioned. Here the change in voltage for each level is  $V_{\rm dc}/3$ .

### C. Nine Level hybrid H-Bridge

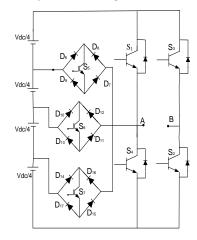

Fig.4. Nine level hybrid H-Bridge

Figure 4 represents the circuit diagram of 9-level hybrid H-Bridge MLI. Here 7 switches are used. The nine level hybrid H-Bridge consists of four symmetrical voltage sources  $V_{\text{dc}}/4$  in each level.

Table III: Switching operation for 9-level hybrid H-Bridge

| Switches to be<br>Turned On    | Voltage<br>level     |

|--------------------------------|----------------------|

| S <sub>2</sub> ,S <sub>4</sub> | 0                    |

| S <sub>2</sub> ,S <sub>7</sub> | V <sub>dc</sub> /4   |

| S <sub>2</sub> ,S <sub>6</sub> | $2V_{dc}/4$          |

| S <sub>2</sub> ,S <sub>5</sub> | $3V_{dc}/4$          |

| S <sub>1</sub> ,S <sub>2</sub> | $V_{dc}$             |

| S <sub>3</sub> ,S <sub>5</sub> | $-V_{dc}/4$          |

| S <sub>3</sub> ,S <sub>6</sub> | -2V <sub>dc</sub> /4 |

| S <sub>3</sub> ,S <sub>7</sub> | -3V <sub>dc</sub> /4 |

| S <sub>3</sub> ,S <sub>4</sub> | -V <sub>dc</sub>     |

The nine level hybrid H-Bridge switching sequence is shown above Table-III. Here the change in voltage from one level to other level is  $V_{dc}/4$ . That means as the number of levels is increasing the dv/dt is decreasing.

# D. Eleven Level Hybrid H-Bridge

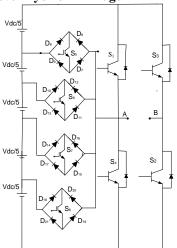

Fig.5. Eleven level hybrid H-Bridge

Fig.5 represents the circuit diagram of an 11-level hybrid H-Bridge MLI. It is seen from the diagram that the number of switching devices needed for this is 8 and 4 diode bridges are used here for the bidirectional operation of switch. The eleven level hybrid H-Bridge consists of five symmetrical voltage sources  $V_{\rm dc}/5$  each.

Table IV. Switching operation for an eleven level hybrid H-Bridge

| Switches to be<br>Turned On    | Voltage<br>level     |

|--------------------------------|----------------------|

| S <sub>2</sub> ,S <sub>4</sub> | 0                    |

| $S_2,S_8$                      | $V_{dc}/5$           |

| $S_2,S_7$                      | $2V_{dc}/5$          |

| $S_2,S_6$                      | $3V_{dc}/5$          |

| $S_2,S_5$                      | $4V_{dc}/5$          |

| $S_1,S_2$                      | $V_{dc}$             |

| $S_{3}, S_{5}$                 | $-V_{\rm dc}/5$      |

| $S_{3,}S_{6}$                  | $-2V_{dc}/5$         |

| $S_3, S_7$                     | $-3V_{dc}/5$         |

| S <sub>3</sub> ,S <sub>8</sub> | -4V <sub>dc</sub> /5 |

| S <sub>3</sub> ,S <sub>4</sub> | -V <sub>dc</sub>     |

The switching table for an eleven level hybrid H-Bridge is represented by Table-IV and the switching sequence for each level is mentioned. The voltage stress (dv/dt) for each level is  $V_{dc}/5$ . Therefore the stress on the switches is very less.

### E. Hardware Implementation.

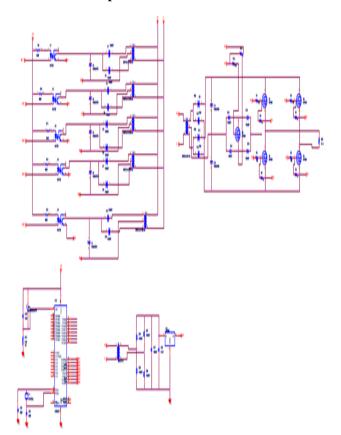

Fig.6. Hardware model of 5- level hybrid H-Bridge.

Figure 6 represents general schematic diagram of hardware model of a 5-level hybrid H-Bridge MLI. By the proper adjustment of the values of input DC voltages and switches we can obtain the operation for 7, 9 and 11 level inverter topologies.

# III. MATLAB MODEL AND SIMULATION RESULTS

Table V. Parameters used in the simulation circuit

| Parameter      | Value          |

|----------------|----------------|

| $V_{dc}$       | 400 volts      |

| Resistive load | 10 KW          |

| RL-Load        | 8 KW<br>6 KVAR |

| Frequency      | 50 HZ          |

### A. Output Results for a 5-level inverter with R-load

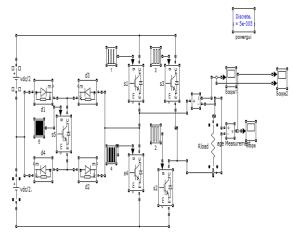

Fig.7. Simulink model of 5- level hybrid H-Bridge MLI.

Fig.7 represents Simulink model of 5-level hybrid H-Bridge MLI for R-load.

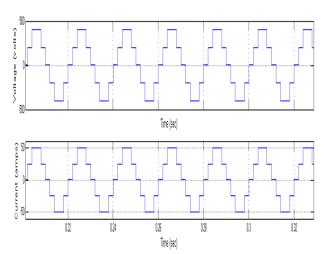

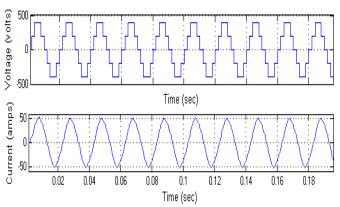

Fig. 8. Output wave forms of a five level hybrid H-Bridge MLI with R-load.

# Simulation and Prototype Implementation of Hybrid H-Bridge MLI with Minimum Switches

Fig.8 represents the output of a five level MLI fed to R-load. Because of resistive load, the current wave follows the voltage wave form.

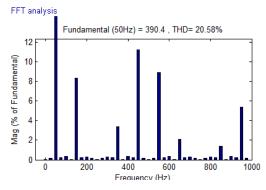

Fig.9. FFT for 5-level output voltage.

Fig.9 represents FFT for the 5-level output of a hybrid H-Bridge inverter. From this THD is 20.58%.

# B. Output Wave Forms for 5-Level Inverter with RL-load

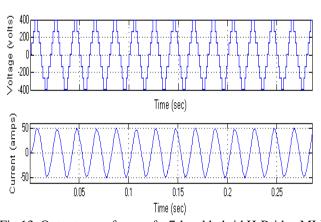

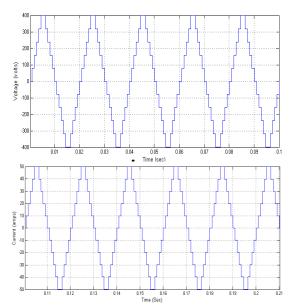

Fig.10. Output wave forms of 5-level hybrid H-Bridge MLI with RL-load.

Fig.10 represents Output wave forms for a five level with RL-load.

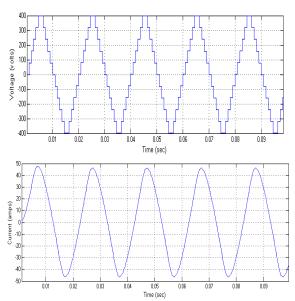

# C. Output Wave Forms for 7-Level Inverter fed R- Load

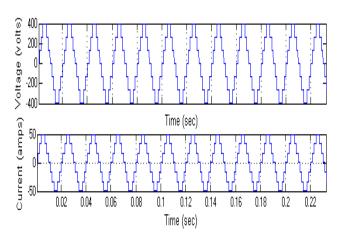

Fig.11. Output wave forms of a 7-level hybrid H-Bridge MLI connected to R-load.

Output waveforms for Voltage & Current of a 7-level hybrid H-Bridge with R-load are mentioned in figure 11. For the same voltage of 400 volts, we could increase the number of voltage levels.

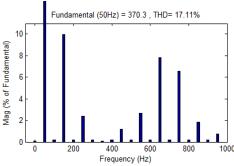

Fig.12. FFT for 7-level output.

Fig.12 represents the FFT for 7-level output voltage. From this THD is decreased to 17.11%.

# D. Output Wave Forms For Seven Level MLI fed RL-load

Fig.13. Output wave forms of a 7-level hybrid H-Bridge MLI with RL-load.

Figure 13 represents the voltage & current waveforms of a 7-level hybrid H-Bridge with RL-load.

### E. Output Wave Forms For 9- Level with R-load

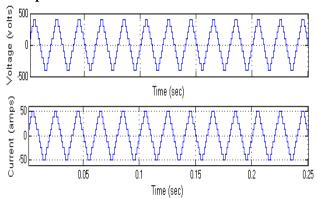

Fig.14. Output wave forms of a 9-level hybrid H-Bridge MLI with R-load.

Figure 14 represents the Output wave forms of a 9-level hybrid H-Bridge MLI with R-load.

# F. Outputs graphs For 9-level Inverter fed RL-load

Fig.15. Output wave forms of a 9- level hybrid H-Bridge MLI fed RL-load.

Fig.15 represents output waveforms of a nine level hybrid H-Bridge MLI fed RL-load.

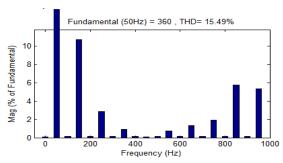

Fig.16. FFT for 9-level output.

Figure 16 represents FFT for 9-level inverter. Here THD is 15.49%

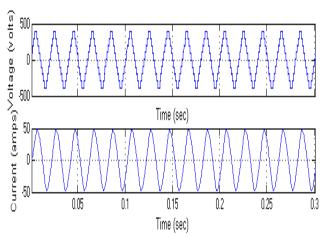

# G. Output graphs for an 11-Level MLI with R-load

Fig.17. Output wave forms of an 11- level hybrid H-Bridge MLI with R-load.

Figure 17 represents voltage & current waveforms of an 11-level hybrid H-Bridge MLI with R-load.

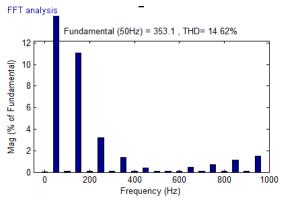

Fig. 18. FFT for eleven level output voltage.

Figure 18 represents the FFT for an 11-level output. In this THD is 14.62%.

# H. Output Wave Forms for Eleven Level RL-load

Fig.19. Output wave forms of a eleven level hybrid H-Bridge MLI with RL-load

Figure 19 represents voltage and current waveforms of an 11-level hybrid H-Bridge MLI with RL-load.

Table VI. THD values presented in different levels of hybrid H-bridge MLI.

| Voltage level | THD%   |

|---------------|--------|

| Five level    | 20.58% |

| Seven level   | 17.11% |

| Nine level    | 15.49% |

| Eleven level  | 14.62% |

Table-VI represents the percentage of THD for 5, 7, 9&11 levels of a hybrid H-Bridge MLI.

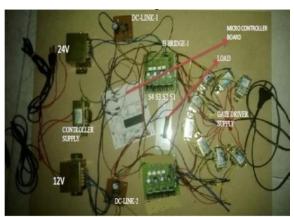

# IV.EXPERIMENTAL RESULTS OF A 5- LEVEL HYBRID H -BRIDGE MLI

Fig.20. Hardware implemented circuit of a five level hybrid H-Bridge.

Hardware model for 5-level hybrid H-Bridge is represented in figure 20. Hardware circuit employs 8051 microcontroller to generate the required control signals. The results and

switching pulses are mentioned below.

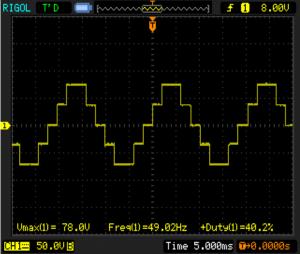

Fig.21. 5-level output of hybrid H-Bridge.

Figure 21 represents the hardware results for 5-level Hybrid H-bridge MLI with frequency 50Hz and Duty ratio 40.2%. Figure 22 shows the gating pulse for switch 1 of a five level

hybrid H-Bridge MLI.

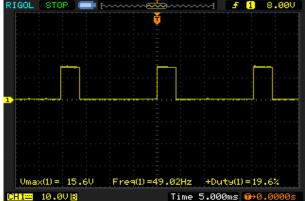

Figure 22. Gating pulse for  $S_1$

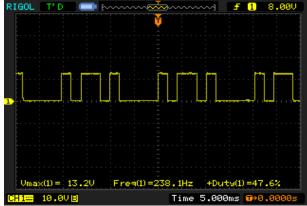

Figure 23. Gating pulse for  $S_2$

Figure 23 represents the gating pulse for switch 2 of a five level hybrid H-Bridge inverter. Figure 24 shows the gating pulse for switch 3 of a five level hybrid H-Bridge MLI.

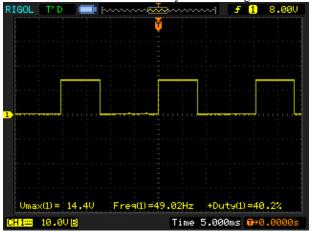

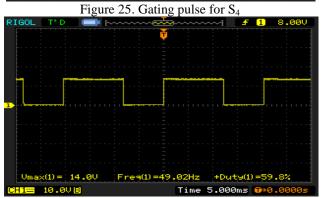

Figure 26. Gating pulse for  $S_5$

Figure 25 represents the gating pulse for switch 4 of a five level hybrid H-Bridge MLI. Figure 26 represents the gating pulse for switch 5 of a five level hybrid H-Bridge MLI. Figure 22 to 26 shows the gate pulses for five level MLI switches (S1-S5). Depending on these gate pulses certain switches will conduct, when gate pulses flows through it.

### **V CONCLUSION**

In conclusion, it is clearly distinguished that the THD for different levels and it is seen that THD gets reduced as the voltage levels are increasing. From the switching tables we can observe that at any interval of time only two switches are conducting, therefore switching frequency is less. The voltage stress (dv/dt) is decreasing as we go for higher level and the dv/dt for an eleven level is  $V_{\rm dc}/5$  which is very low and results less stress on the switches. We can also strongly confirm that, the requirement of switches is less in this configuration when compared to CHB configuration. Hence, gate driver circuit required and the protection arrangement are less, which leads to low cost. The FFT analysis for voltage is obtained and the THD values for each level are observed. A prototype is also developed for a five level Hybrid H-Bridge and the results are displayed.

### **REFERENCES**

- S. Kumar, "A Hybrid Model of Solar-Wind Power Generation System", IJAREEIE, vol. 2, no. 8, pp. 4107-4116, Aug 2013.

- S. Ranjan, "Design of Standalone Hybrid Biomass & PV System of an Off-Grid House in a Remote Area", IJERA, vol. 3, no. 6, pp. 433-437, Nov-Dec 2013.

- E. Najafi and A. Yatim, "Design and implementation of a new multilevel inverter topology", IEEE Trans. Ind. Electron., vol. 59, no. 11, pp. 4148-4154, Nov 2012.

- B. P. McGrath and D. G. Holmes "A decentralized controller architecture for a cascaded h-bridge multilevel converter", IEEE Trans. Ind. Electron., vol. 61, no. 3, pp. 1169-1178, Mar. 2014

- A .Ramesh and O. Chandra Sekhar "A Novel Three Phase Multilevel Inverter with Single DC Link for Induction Motor Drive Applications" IJECE, pp. 2088-8708, Jan 2018.

- A.Ramesh and O. Chandra Sekhar "A Simplified PWM Technique for Reduced Switch Count Multilevel Inverter" IJEECS, pp 2502-4752, October 2017.

- A.Ramesh and O. Chandra Sekhar "Simulation Analysis and Experimental Validation of Symmetrical and assymetrical cascaded H- Bridge Multi Level inverter for PV Application" JEE, 2016.

- S. Rivera, S. Kouro, et al., "Multilevel direct power control-a generalized approach for grid-tied multilevel converter application", IEEE Trans. Power Electron., vol. 29, no. 10, pp. 5592-5604, Oct. 2014.

#### **AUTHORS PROFILE**

**Dr. A. Ramesh** received his B. Tech in Electrical &Electronics Engineering and M.Tech in High Voltage Engineering from JNTU College of Engineering, Kakinada, Andhra Pradesh, India. He obtained his Ph. D from K.L. University India. His research interests are power electronics and electrical drives. Currently he is working as a Professor in the Department of Electrical and Electronics Engineering, Aditya college of Engineering,

Surampalem, A.P. India. He is a life member of the Indian Society for Technical Education.

**Dr. K V S Ramachandra Murthy** born in Kakinada in 1972. He obtained his UG and PG in Electrical Engineering from NIT, Jamshedpur in 1994 and 2002 respectively. He obtained his Ph. D. from JNTUK, Kakinada in 2013. His research interests are Power System Operation, Control and Stability, and Application of Artificial Intelligence Techniques in Power Distribution System. He has published 35 research papers

in various Journals and Conferences. He is currently working as Director (Research & Development), Aditya Group of Engineering Colleges, Surampalem, Kakinada.

Mr. B.V.S.S.S.Gopal completed his B. Tech in Electrical &Electronics Engineering and M.Tech in Power Electronics. His research interests are power electronics and electrical drives. Currently he is working as an Assistant Professor in the Department of Electrical and Electronics Engineering, Aditya college of Engineering, Surampalem, A.P. India. He is a life member of the Indian Society for Technical Education