# VLSI based Error Correction Code Using Fault-tolerant Parallel FFTs

# SakhamuriSravanthi, Rajendra Prasad Somineni

The difficulty in the signal processing and Abstract: communication systems increase year by year. This results in the on demand for scaling and integration with the help of advanced CMOS technologies. Soft errors are reliability thread on modern digital world which explains the need of protection against errors in digital circuit applications. In some applications, techniques like Algorithm based fault tolerance (ABFT) are used to detect and correct error with the help of algorithm properties. As the filters are the basic building blocks in most of systems, FFTs are used with the protection scheme using parseval checks which detects and corrects errors. The proposed technique consume low power. A technique is proposed using parseval checks to protect the circuits from single bit errors and is further improved for multi bit errors detection and correction and are evaluated in area and delay parameters.

Index Terms: ECC, ABFT, softerrors, TMR, Parseval Checks.

# I. INTRODUCTION

The check bit clusters, much the same as the information bit exhibits, ought to be tried judiciously for a similar flaw models if solid mistake rectification is to be safeguarded. Quick Fourier change is utilized to change over a sign from time area to recurrence and this is required with the goal that you can see the recurrence parts present in a sign. A deficiency tolerant framework should almost certainly endure blames in the framework itself as well as flaws in the application programs. So as to make a flaw tolerant framework for a specific application, the adaptation to non-critical failure requests of the objective application should initially be recognized. At that point, the proper adaptation to internal failure techniques must be utilized so as to meet the general adaptation to non-critical failure prerequisites.

# **II. RELATED WORKS**

Error detection systems permit recognizing such blunders, while blunder remedy empowers reproduction of the first information by and large. Over the most recent couple of decades [1], recuperation square has been treated by numerous specialists as an adaptation to a non-critical failure

Revised Manuscript Received on October 30, 2019.

- \* Correspondence Author

- Sakhamuri Sravanthi\*, Research Scholar, Department of ECE, Shri JJT University, Jhunjhunu, Rajasthan, India.

**Rajendra Prasad Somineni\***, Professor, Department of ECE, VNR Vignana Jyothi Institute of Engineering an Technology, Hyderabad, India.

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an <u>open access</u> article under the CC BY-NC-ND license (<u>http://creativecommons.org/licenses/by-nc-nd/4.0/</u>)

framework. Velardi and Ciciani (1983) considered the recuperation obstruct for correspondence frameworks. Appropriated execution of recuperation obstructs for uniform of equipment and treatment programming issues progressively applications [2] were examined by Rossi and Simone (1984) and Kim and Welch (1989). Nicola and Goyal (1990) displayed corresponded failures [3] and network blunder recuperation in multi-version programming. Immense writing can be found on different equipment and programming excess methods and dependability displaying for repetitive frameworks. Kumar et al. (1986) considered the unwavering quality investigation of a two-unit excess system [4] with the basic human mistake. Grosspietsch (1989) proposed the plans of dynamic repetition for deficiency tolerant in arbitrary access recollections. Executing adaptation to internal failure by means of particular redundancy [5] with correlation was finished by Yinong and Chen (1992). Venkateswaran et al. (2002) dissected excess based shortcoming recognition of gyrators in rocket applications [6]. Infusing deficiencies at the physical level has been finished by either focusing on the equipment with natural parameters or by a change of the stick level qualities. The principal technique has been utilized by Karlsson and Gunneflo by inciting transient delicate errors [7] with overwhelming particle radiation.

# **II. EXISTING METHODS**

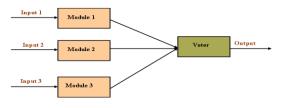

# 1. Triple Modular Redundancy

The most widely recognized type of inactive equipment excess is a triple modular redundancy (TMR). In this kind of repetition, the segments are in triplicate to play out a similar calculation in parallel. Larger part casting a ballot is utilized to discover the right outcome. On the off chance that one of the modules falls flat, the greater part voter will cover the shortcoming by perceiving the consequence of the staying two flaw free modules as right. A TMR framework can veil just a single module deficiency. A disappointment in both of the rest of the modules would make the voter produce an incorrect outcome. TMR is generally utilized in applications where a considerable increment in dependability is required for a brief period.

Figure 1 Triple modular redundancy

Val Journal

Retrieval Number F8258088619/2019©BEIESP DOI: 10.35940/ijeat.F8258.088619 Journal Website: <u>www.ijeat.org</u>

Published By: Blue Eyes Intelligence Engineering & Sciences Publication

# 2. LUT based Checker

The LUT is an exhibit that replaces runtime calculation with a less complex cluster ordering activity. The investment funds as far as the handling time can be critical, since recovering an incentive from memory is frequently quicker than experiencing a 'costly' calculation or information/yield task. The tables might be pre-determined and put away in static program stockpiling or pre-gotten as a major aspect of a program's introduction stage (memorization), or even put away in equipment in application explicit stages.

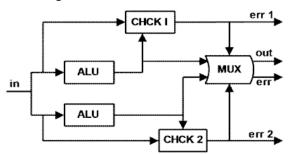

#### 3. Duplex Architecture with Checkers

The data sources are given to both functional units (FU). On the off chance that an utilitarian unit has an issue, or a shortcoming has happened in one of the practical units, the checker conveys a comparing blunder (fail) signal. The checker plays out the capacity of checking if the yield from the practical unit is the right one. Both the yields of the utilitarian unit are likewise given to the multiplexer (mux). The mux gives the right yield dependent on the location in the blunder signal. For instance, on the off chance that any of the blunder signals from the checker demonstrates '0', at that point the out sign from the mux is the right yield, and the fail sign will be '0'. In the event that both the blunder signals from the checker show '1', at that point the out sign from the mux is an inaccurate yield, and the 'fail' signal from the mux indicates '1'. Henceforth, any flaw in the module can be found and reconfigured.

Figure 2 Duplex architecture with checker for ALU 4. Parallel FFT Protection using ECCs:

**III. PROPOSED WORK**

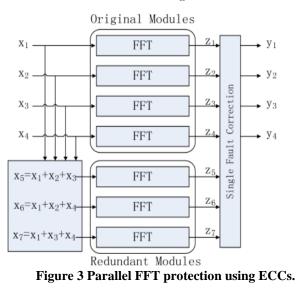

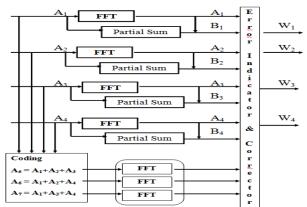

#### (Parity-PS-ECC fault-tolerant parallel FFTs)

The Fig.6 depicts the new strategy. The procedure broke down in the past work has certain constraint because of the intricacy of taking care of bigger number of FFTs and Sum of Squares square. For instance when the mistake happens in A1 and A2 then it tends to be distinguished by the fractional summation utilized independently for FFT squares. The main check condition is chosen so that the both blunder square flag are absent.

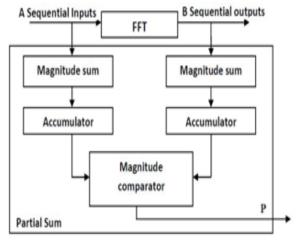

**Figure 4Implementation of Partial Summation**

The system examined in the past work has certain impediment because of the multifaceted nature of taking care of bigger number of FFTs and Sum of Squares square. Rather than utilizing Sum of Squares, Partial Summation (PS) is utilized for ascertaining its equality at the info and the yield side of the FFT. It totals all conceivable hub estimations of 4-point FFT alongside the fidget factors. Duplication activity which prompts the multifaceted nature in Figure 5. outlines the Parity Partial Summation obstruct for less blunder inclined applications. For the ECC method, the security of these components was examined. On account of the excess or equality FFTs, a blunder will have no impact as it won't engender to the information yields and won't trigger a revision. On account of SOS checks, a mistake will trigger a revision when entirely is no blunder on the FFT. This will cause a superfluous remedy yet will likewise deliver the right outcome. At long last, blunders on the discovery and amendment squares can engender mistakes to the yields.

Figure 5 Parity-PS-ECC fault-tolerant parallel FFTs

Published By:

& Sciences Publication

#### **RESULTS and DISCUSSIONS** IV.

### **Table1: Resource utilization for 4 parallel FFTs**

| Design<br>summary | Parallel<br>SOS ECC | Parity<br>SOS ECC | Parity<br>PS ECC |

|-------------------|---------------------|-------------------|------------------|

| Slices            | 112                 | 87                | 70               |

| Flip flops        | 32                  | 25                | 21               |

| LUTs              | 191                 | 159               | 125              |

| Delay (ns)        | 13.935              | 18.02             | 3.27             |

| Power(µw)         | 246                 | 252               | 243              |

It is inferred that the Table 1 shows that various parameters which have been analyzed and the comparative results of 4-Parallel FFTfurnish the best performance fault tolerant error free result.

Table 2: Resource utilization for 6 parallel FFTs

| Design<br>summary | Parallel<br>SOS ECC | Parity<br>SOS ECC | Parity<br>PS ECC |

|-------------------|---------------------|-------------------|------------------|

| Slices            | 211                 | 862               | 152              |

| Flip flops        | 295                 | 414               | 152              |

| LUTs              | 270                 | 1443              | 185              |

| Delay (ns)        | 13.935              | 10.125            | 3.102            |

| Power(µw)         | 258                 | 261               | 234              |

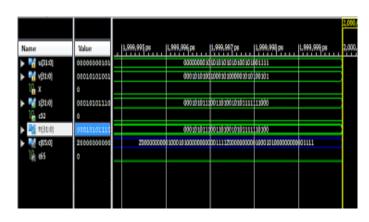

Table 2 demonstrates the relative aftereffects of 6-Parallel FFT Parity-SOS-ECC with two new strategies. Impressive improvement additionally accomplished as far as power and postponement. The other proposed strategy Parity Partial Summation ECC results again additionally improved equipment structure utility contrasted with Parallel Partial Summation ECC. From this examined view to decrease power and structure territory of the new proposed strategies utilizing to the equality Partial Summation ECC than existing halfway check ECC method. The sources of info are given to the parallel FFTs, yields created from these are encouraged to the equality SOS-ECC to identify and address the mistakes. The principle advantage over the main equality SOS plan is to decrease the quantity of SOS checks required. The blunder area procedure is equivalent to for the ECC plan and revision is as in the equality SOS conspire. The outcomes demonstrate that the subsequent method, which uses equality FFT and a lot of SOS watches that structure an ECC, gives the best outcomes as far as execution multifaceted nature. As far as blunder insurance, flaw infusion tests demonstrate that the ECC plan can recuperate every one of the mistakes that are out of the resistance extend. Fig 7 shows the simulation of the same. Simulation Results for Parity-PS-ECC Fault-Tolerant Parallel FFTs is represented by Fig 8.

Figure 6 Simulation Results for Parity-SOS-ECC **Fault-Tolerant Parallel FFTs**

Figure 7 Simulation Results for Parity-PS-ECC Fault-Tolerant Parallel FFTs.

In the proposed method the errors present in the original module FFTs it can be detected by using partial summation. The detected error in can be corrected by using ECC approach as a redundant module. Fig 9 shows the error part, Fig 10 shows the corrupted part detection after that final corrected output using partial summation shown in Fig 11.

Figure 8 Partial summation methods -error part

**Figure 8 Corrupted Part Detection**

**Figure 9 Final Error Free Output Waveform**

Published By:

& Sciences Publication

# V. CONCLUSION

The protection of parallel FFTs implementation against soft errors has been studied. A technique has been proposed and evaluated. The proposed technique is based on combining error correction codes and partial summation. The proposed techniques have been evaluated both in terms of implementation complexity and speed (delay). The results show that the proposed technique, which uses a parity FFT and a set of Parseval Summation checks that form an ECC, provides the best results in terms of implementation complexity and has low power consumption.

# REFERENCES

- 1. Velardi, P. and Ciciani, B. (1983): Recovery blocks for communicating systems. Microprocessing and Microprogramming, Vol. 11, No. 5 pp. 287-294

- 2. Rossi, G. P. and Simone, C. (1984): A multitasking operating system with explicit treatment of recovery points. Microprocessing and Microprogramming, Vol. 14, No. 2 pp. 55-66.

- 3 Nicola, V. F. and Goyal, A. (1990): Modeling of correlated failures and community error recovery in multi version software. IEEE Transactions on Engineering, Vol. 16, No. 3, pp. 350-359.

- 4. Kumar, A., Agarwal, M. L. and Garg, S. C. (1986): Reliability analysis of a two-unit redundant system with critical human error. Microelectronics and Reliability, Vol. 26, pp. 867-871.

- 5. Grosspietsch, K. E. (1989): Schemes of dynamic redundancy for fault tolerant in random access memories. Microelectronics and Reliability, Vol. 29, No. 6, pp. 1098.

- Yinong, C. and Chen, T. (1992): Implementing fault-tolerance via 6. modular redundancy with comparison. Microelectronics Reliability, Vol. 32, No. 1-2, pp. 287-288.

- 7 S. Pontarelli, G. C. Cardarilli, M. Re, and A. Salsano, "Totallyfault tolerant RNS based FIR filters", in Proc. 14th IEEE Int.On-Line Test Symp. (IOLTS), Jul. 2008, pp. 192-194.

Published By: